Register Transfer Language (RTL क्या है? )

Register Transfer Language (RTL) एक symbolic notation या representation method है, जिसका उपयोग CPU (Central Processing Unit) के अंदर मौजूद registers के बीच data transfer और micro-operations (जैसे arithmetic, logical, shift operations) को describe करने के लिए किया जाता है।

Table of Contents

ToggleKey Points

- RTL CPU के internal operations को represent करती है।

- यह register-to-register data transfer को clearly show करती है।

- RTL में micro-operations जैसे ADD, SUB, AND, OR, SHIFT आदि explain किए जाते हैं।

- RTL में arrow symbol (←) का use data transfer को show करने के लिए होता है।

- Instruction Cycle (Fetch–Decode–Execute) को समझने में RTL बहुत helpful है।

- Control Unit design और timing analysis में RTL का use किया जाता है।

- RTL user-oriented language नहीं है, hardware-oriented notation है।

Example

R3 ← R1 + R2

- R1 और R2 का addition होकर result R3 register में store होगा।

Need of Register Transfer Language

(RTL की आवश्यकता)

Computer के अंदर होने वाली processing हमें directly दिखाई नहीं देती। CPU के भीतर data लगातार registers, ALU और Control Unit के बीच move करता रहता है। इन internal activities को clear, systematic और understandable तरीके से explain करने के लिए Register Transfer Language (RTL) की आवश्यकता रखी गई।

RTL की आवश्यकता

- CPU के Internal Working को समझाने के लिए

- RTL यह बताती है, कि instruction execute होते समय data किस register में है, और कहाँ transfer हो रहा है।

- Register-to-Register Data Transfer को Represent करने के लिए

- Registers के बीच data movement को simple symbolic form में दिखाने के लिए RTL जरूरी है।

- Example : R2 ← R1

- Micro-Operations को Describe करने के लिए

- Arithmetic, logical और shift operations (ADD, SUB, AND, OR आदि) को explain करने में RTL मदद करती है।

- Instruction Cycle को Explain करने के लिए

- RTL instruction fetch, decode और execute process को आसानी से समझने योग्य बनाती है।

- Control Unit के Design में सहायता के लिए

- Control Unit यह decide करती है, कि कौन सा register active होगा और कब operation होगा, RTL इसमें clear guidance देती है।

- Timing और Sequence को Show करने के लिए

- RTL clock signals के साथ यह बताती है कि कौन-सा operation किस time पर होगा।

- Example : T1: MAR ← PC

- Computer Architecture की Complexity को Reduce करने के लिए

- Complex hardware operations को simple notation में convert करके learning आसान बनती है।

Basic Concept of RTL

RTL दो मुख्य concepts पर आधारित है :

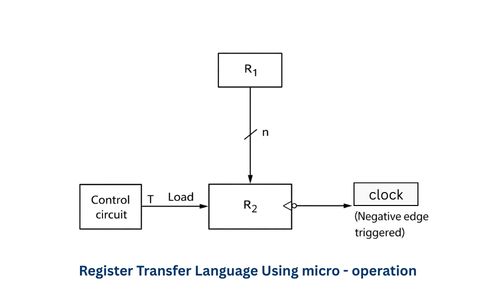

1. Register Transfer (Data Transfer between Registers)

- CPU के अंदर data एक register से दूसरे register में transfer होता रहता है।

- RTL इस transfer को arrow symbol (←) की मदद से show करती है।

Example

R1 ← R2

- R2 register का data, R1 register में copy हो गया।

2. Micro-Operations

- Micro-operations वो smallest operations होते हैं, जो CPU hardware level पर perform करता है, जैसे : Addition, Subtraction, Logical AND / OR, Shift operations

- RTL इन micro-operations को registers के साथ combine करके represent करती है।

Example

R3 ← R1 + R2

- R1 और R2 का addition होकर result R3 में store होता है।

Notation Used in Register Transfer Language (RTL)

Notation / Symbol | Meaning | Explanation / Use | Example |

← | Data Transfer | Source register से destination register में data copy करना | R1 ← R2 |

+ | Addition | Two registers के data को add करना | R3 ← R1 + R2 |

− | Subtraction | One register से दूसरे का data subtract करना | R4 ← R3 − R1 |

AND | Logical AND | Bitwise AND operation perform करना | R1 ← R2 AND R3 |

OR | Logical OR | Bitwise OR operation perform करना | R1 ← R2 OR R3 |

NOT | Logical NOT | Bits को invert करना (1→0, 0→1) | R2 ← NOT R1 |

SHL / << | Shift Left | Bits को left side shift करना | R1 ← R1 << 1 |

SHR / >> | Shift Right | Bits को right side shift करना | R2 ← R2 >> 1 |

If (Condition) | Conditional Transfer | Condition true होने पर ही operation execute करना | If (Z=1) then PC ← IR |

: | Timing Symbol | Clock cycle या timing indicate करना | T1: MAR ← PC |

Memory[ ] | Memory Access | Memory location से data read/write करना | MDR ← Memory[MAR] |

PC + 1 | Increment | Program Counter को next instruction की ओर move करना | PC ← PC + 1 |

Advantages of Register Transfer Language (लाभ)

- CPU की Internal Working को Clearly Explain करता है

- RTL CPU के अंदर registers, ALU और Control Unit के बीच होने वाली activities को step-by-step दिखाती है।

- इससे यह समझना आसान हो जाता है कि instruction execute कैसे होती है।

- Register-to-Register Data Transfer को Simple बनाता है

- RTL arrow symbol (←) के माध्यम से data movement को बहुत clearly show करती है।

- Complex hardware operations भी simple notation में समझ आ जाते हैं।

- Micro-Operations को समझने में मदद करता है

- Arithmetic, logical और shift operations को RTL आसानी से represent करती है।

- इससे ALU की working clear हो जाती है।

- Instruction Cycle को Step-by-Step समझाने में Helpful

- Fetch, Decode और Execute cycle को RTL के बिना समझना मुश्किल होता है।

- RTL हर stage को clearly break करके दिखाती है।

- Control Unit Design में सहायता करता है

- Control Unit को यह decide करना होता है कि: कौन सा register active होगा, कब data transfer होगा

- RTL इन decisions को clearly define करती है।

- Hardware Complexity को Reduce करता है

- CPU के complex internal behavior को logical steps में convert करके RTL learning को आसान बनाती है।

- Timing और Sequencing को Show करता है

- RTL clock cycles के साथ operations को represent कर सकती है।

Limitations of Register Transfer Language (सीमाएँ)

- User-Oriented Language नहीं है

- RTL end-users के लिए नहीं बनी है।

- Normal users या programmers directly RTL में program नहीं लिख सकते।

- High-Level Programming के लिए Suitable नहीं

- RTL application development के लिए use नहीं होती, जैसे: Web development, Mobile apps, Database applications यह केवल hardware level तक limited है।

- Real Hardware Implementation नहीं दिखाती

- RTL conceptual representation है।

- Actual hardware wiring, circuits और electrical behavior इसमें include नहीं होते।

- Beginners के लिए Initially Difficult हो सकती है

- Students को registers, ALU और control signals का basic knowledge होना जरूरी है।

- Without fundamentals, RTL confusing लग सकती है।

- Large Systems के लिए Lengthy हो जाती है

- Complex instructions और processors के लिए RTL description बहुत लंबी और complex हो सकती है।

- Error Handling या User Interaction नहीं दिखाती

- RTL सिर्फ data transfer और operations तक limited रहती है।

- User input, output handling या error messages को describe नहीं करती।

- Direct Execution Possible नहीं

- RTL executable language नहीं है। इसे directly computer पर run नहीं किया जा सकता।

Bus & Memory Transfer

Bus Transfer

Computer system में जब एक से ज्यादा registers होते हैं, तो उनके बीच data transfer के लिए Bus System का use किया जाता है। Bus एक common communication path है, जिससे multiple registers आपस में data share करते हैं।

Register transfer को implement करने के दो main methods होते हैं :

- Bus Transfer using Multiplexer

- Bus Transfer using Three-State Bus Buffers

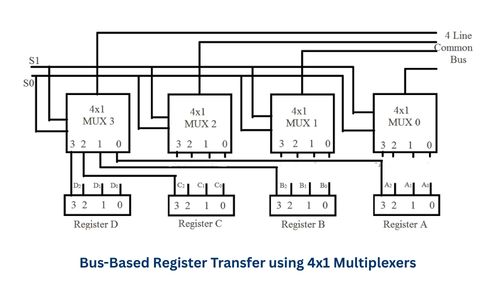

1. Bus Transfer using Multiplexer

Computer Architecture में जब एक से अधिक Registers होते हैं, और सभी को एक common bus के माध्यम से data भेजना होता है, तब Bus Transfer using Multiplexer technique का उपयोग किया जाता है। इस method में Multiplexer (MUX) की मदद से किसी एक register का data select करके bus पर transfer किया जाता है।

- Multiplexer एक combinational logic circuit होता है जो multiple input lines में से किसी एक input को select करके output पर भेजता है Selection का काम Select Lines करती हैं।

Working of Bus Transfer using Multiplexer

- Control Unit select lines generate करती है

- Select lines decide करती हैं कि कौन सा register active होगा

- Selected register का data multiplexer से होकर bus पर आता है

- Destination register bus से data receive करता है

Advantages of Bus Transfer using Multiplexer

- Design simple और clear होता है

- Control signals को generate करना आसान होता है

- Bus conflict की problem नहीं होती

- Small-scale systems के लिए यह method suitable होती है

Limitations of Bus Transfer using Multiplexer

- Registers की संख्या बढ़ने पर hardware cost बहुत ज्यादा हो जाती है

- Large-scale systems में multiplexers का design complex हो जाता है

- Power consumption comparatively ज्यादा होता है

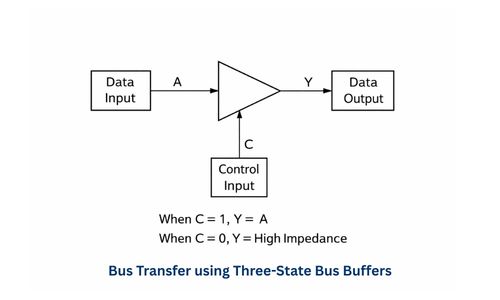

2. Bus Transfer using Three-State Bus Buffers

Bus Transfer using Three-State Bus Buffers एक method है जिसमें CPU के registers और common bus के बीच Three-State Buffers का use किया जाता है।

- Three-State Buffer के तीन states होते हैं:

- 0 → Logic low

- 1 → Logic high

- Z (High Impedance) → Buffer disconnected, bus से कोई connection नहीं

High Impedance state की वजह से एक time में केवल एक register ही bus drive कर सकता है, जिससे bus conflict avoid होता है।

Working of Three-State Bus Buffer

- हर register की output bus से three-state buffer के माध्यम से connect होती है।

- Control signal decide करता है कि buffer enable होगा या disable (Z state) रहेगा।

- केवल एक buffer enable होगा और उसका data bus पर transfer होगा।

Advantages of Three-State Bus Buffers

- Multiplexer की तुलना में Hardware cost कम होती है

- Large systems के लिए suitable और scalable है

- Multiple registers के साथ bus design simple रहती है

- CPU design में high flexibility मिलती है

- नए registers add करना आसान है

Limitations of Three-State Bus Buffers

- Control logic complex होती है

- दो buffers एक साथ enable हो जाएँ, Bus conflict हो सकता है

- Timing पर careful ध्यान रखना पड़ता है

- Direct RTL execution possible नहीं है

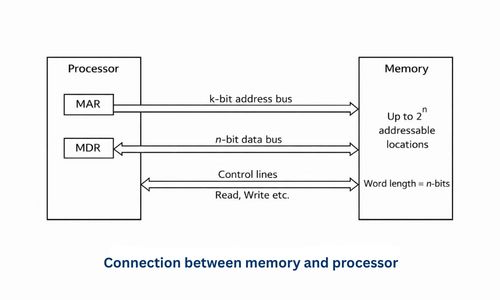

Memory Transfer

Memory Transfer वह process है, जिसमें data या instruction CPU के registers और main memory (RAM) के बीच move किया जाता है।

- Memory → Register : Data read करना

- Register → Memory : Data write करना

Types of Memory Transfer

1. Memory Read (Memory → Register)

Memory से CPU के register में data या instruction को लाना Memory Read कहलाता है।

RTL Representation

MAR ← Address ; Select memory location

MDR ← Memory[MAR] ; Fetch data from memory to MDR

2. Memory Write (Register → Memory)

CPU के register में stored data को Memory में भेजना Memory Write कहलाता है।

RTL Representation

MAR ← Address ; Select memory location

MDR ← R1 ; Load data to write

Memory[MAR] ← MDR ; Store data into memory

3. Memory-to-Memory Transfer (Optional / Some CPUs)

Direct memory-to-memory data transfer बिना CPU register के भी possible होता है, लेकिन यह slow और rare है।

RTL Representation

Temp ← Memory[1000]

Memory[2000] ← Temp

Advantages of Memory Transfer

- CPU और Memory के बीच data communication possible बनाता है

- RTL और timing signals के माध्यम से step-by-step data transfer समझा जा सकता है

- Instruction execution में essential होता है

Disadvantages of Memory Transfer

- Memory access registers की तुलना में slower होती है

- Timing signals और control logic पर dependency होती है

- Improper control होने पर bus conflict हो सकता है

निष्कर्ष (Conclusion)

Register Transfer Language (RTL) CPU और Computer Architecture का एक fundamental concept है। यह CPU के अंदर registers, ALU और Control Unit के बीच data movement और micro-operations को symbolic form में represent करता है।

- RTL hardware-oriented notation है, user/programmer oriented नहीं।

- यह arrow symbol (←) और operators (+, −, AND, OR, SHL, SHR) का उपयोग करके data transfer और micro-operations को clearly दिखाती है।

- RTL के माध्यम से हम Instruction Cycle (Fetch, Decode, Execute) को step-by-step समझ सकते हैं।

- Bus और Memory Transfers के लिए भी RTL notation का use होता है, जिससे CPU और memory के बीच data communication समझना आसान हो जाता है।

- Multiplexer और Three-State Bus Buffer techniques का use करके register-to-register और memory transfers को implement किया जाता है।

- RTL से CPU design, timing analysis और control unit design में मदद मिलती है।

अक्सर पूछे जाने वाले प्रश्न (FAQ)

Q1. Register Transfer Language (RTL) क्या है?

- RTL एक symbolic notation है जो CPU के अंदर registers और micro-operations के बीच होने वाले data transfers को represent करता है।

Q2. RTL की आवश्यकता क्यों है?

- CPU की internal working, instruction cycle, micro-operations, timing और sequencing को clear और understandable explain करने के लिए।

Q3. RTL में कौन-कौन से operations show किए जा सकते हैं?

- Data Transfer (←)

- Arithmetic (+, −)

- Logical (AND, OR, NOT)

- Shift (SHL/<<, SHR/>>)

- Conditional (If condition)

- Memory Access (Memory[ ])

- Increment (PC ← PC + 1)

Q4. Bus Transfer क्या है और इसे implement कैसे किया जाता है?

- Bus Transfer registers के बीच common communication path (bus) का use करके data transfer करने की method है।

- Implementation Methods:

- Multiplexer – Selected register data bus पर send करता है।

- Three-State Bus Buffer – केवल enabled buffer data bus पर भेजता है; high-impedance state से bus conflict avoid होता है।

Q5. Memory Transfer क्या है?

- Memory Transfer में data CPU के registers और Main Memory के बीच move होता है।

- Memory Read: Memory → Register

- Memory Write: Register → Memory

- Memory-to-Memory Transfer: Optional, slow और rare

Q6. Multiplexer और Three-State Bus Buffer में क्या अंतर है?

| Feature | Multiplexer | Three-State Bus Buffer |

|---|---|---|

| Hardware Cost | High with many registers | Relatively Low |

| Scalability | Less suitable for large systems | Highly scalable |

| Bus Conflict | Rare due to selection logic | Possible if control fails |

| Control Logic | Simple | Complex |

https://computerhindinotes.com/role-of-computer-registers-functions-types-and-advantages/